前几天在一家做逻辑设计的公司里做了一道笔试题,有些心塞。用Verilog HDL描述三分频的实现。说实话,一开始我是拒绝的。我之前做过分频实验,几百毫秒的LED闪烁,控制蜂鸣器发出不同音频段的声音,都是分频实验的例子。现在想想,基本都是偶数分频。

一开始我是6分频的基础上做了2倍频,结果描述内容过于繁琐,以致写着写着就放弃挣揣,没经历过得东西是编不出来的。回来在网上找到了许多解决奇、偶数的分频实现。说实话,理论知识还是比较多的,就是代码实现有些欲盖迷彰,我抄写下来验证几乎都是错的。好在理论知识分析透彻,而后我自己尝试编写了一下,写下作为分享。

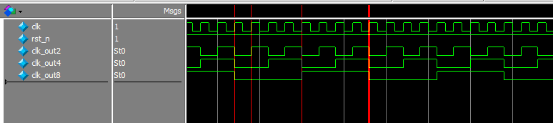

偶数分频,例如二分频,简单讲就是一个时钟周期的高电平和一个时钟周期的低电平。设reg cnt,默认一位,每一个时钟上升沿自加1,则cnt的电平变化就可以作为二分频输出。由此,设reg [3:0] cnt,则cnt[1],cnt[2],cnt[3]对应4/8/16分频。这些操作,我们常常在led延时处理上用到。

语言描述如下:

module test2_1(clk,rst_n,clk_out2,clk_out4,clk_out8);

input clk;

input rst_n;

output clk_out2;

output clk_out4;

output clk_out8;

reg [2:0]cnt;

always@(posedge clk or negedge rst_n)

if(!rst_n)

cnt

else

cnt

assign clk_out2 = cnt[0];

assign clk_out4 = cnt[1];

assign clk_out8 = cnt[2];

endmodule

另类偶数分频如6/10/12分频,可在前3/5/6个整数周期处理输出高/低电平,后3/5/6个整数周期取反,操作相对简单,可实现输出为占空比为1:1的分频信号。占空比不等的情况就更简单。

关键语言描述如下: (N=6)

if(cnt

cnt

end

else begin

cnt

clk_out

End

在设计中,我处理为cnt

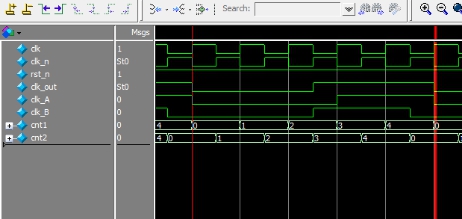

奇数分频占空比为1:1的实现比较复杂,以5分频为例,我采用两个计数器,一个计数器在时钟上升沿触发计数,另一个计数器在时钟下降沿触发计数(或clk_n = ~clk)。各自控制产生一个5分频信号,调节占空比为3:2(容易)。第一个5分频比第二个5分频快半个周期,两个信号取或,完美将占空比分配为1:1,通俗点说,就是3-0.5 = 2+0.5。

此时,我也遇到了cnt

因为上升沿和赋值几乎一条线,我没有混淆是先采集还是先赋值,而是会纠结于多算一个周期或少算一个周期。我还发现自己的逻辑设计不熟练导致与理想效果还是有差距的。调试时,花在逻辑优化的时间较长,另外在后仿真中cnt始终为Z态,不便于我观察,这是我的疑惑,也是接下来要解决的吧。

备注:我会在智慧科技(优先)、EDN、电子产品世界更新内容,信息不涉及商业用途。

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。